This is a guide to correctly activate the FPGA2SDRAM Interface (we refer to it as f2sdram) currently being included as a feature in the Cyclone V SoC devices. This work is implemented on a DE10 Nano board but should be easily extended to all other devices using the same family chip.

First of all we are working with this base setup,

- Linux Console (kernel 4.5) v1.3.

- DE10-Nano_v.1.2.4_HWrevAB_SystemCD Example files.

- Quartus Prime 16.1

- «DE10_NANO_SoC_GHRD» as base project.

Testing the Interface

We should start just compiling the base GHRD project on Quartus, upload the rbf file to the sdcard booting the board and see if f2sdram is working by default. To test the interface we could use the f2sdram_only_master (JTAG to Avalon Master Bridge) IP Core already working in the project to test the f2sdram connectivity.

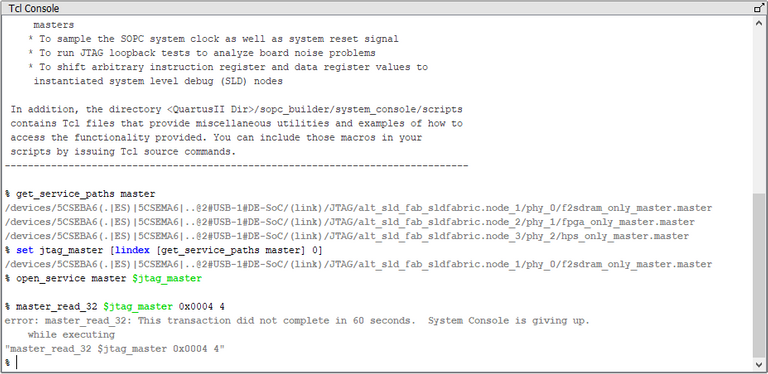

To do this we could go to Qsys ➡️ System Console. Here we could see a list of "JTAG services" currently working and starting the corresponding one. With this we could test the connectivity to the interface. A list of commands useful to achieve this could be seen here.

get_service_paths master

set jtag_master [lindex [get_service_paths master] 0]

##Cuidado con elegir el indice para set jtag_master, debe coincidir

open_service master $jtag_master

master_write_32 $jtag_master 0x0000 1

master_read_32 $jtag_master 0x0004 4

Could be seen that interface isn't working when write and read commands finish with no response at all. This is what I get when testing it on my board.

Modifying the Project

After extensive testing and some useful post found on Altera foums platform I came to the conclusion that f2sdram is simply not activated by default and is needed some extra tweaking to get it working. This is a summary of steps but you could find more info looking at references later.

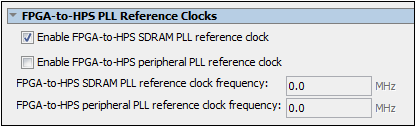

Using Qsys, modify the HPS IP Core and activate a special clock for the f2sdram — and wire a clock to it —.

Save and compile the project under Quartus.

Open SoC EDS (as admin) and go to the project root folder.

Run make preloader.

Run make sd-update-preloader.

$ make sd-update-preloader alt-boot-disk-util -p software/preloader/preloader-mkpimage.bin -a write -d k Altera Boot Disk Utility Copyright (C) 1991-2014 Altera Corporation Altera Boot Disk Utility was successful.Upload the new rbf file to the sd card.

If everything went fine you should have your sd card with a new preloader. Also we have a rbf file in the sd card which uses the f2sdram interface... this is a must since it can't get activated once Linux already started.

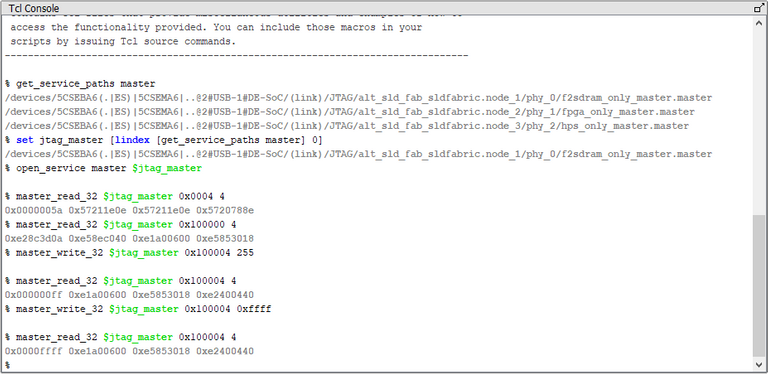

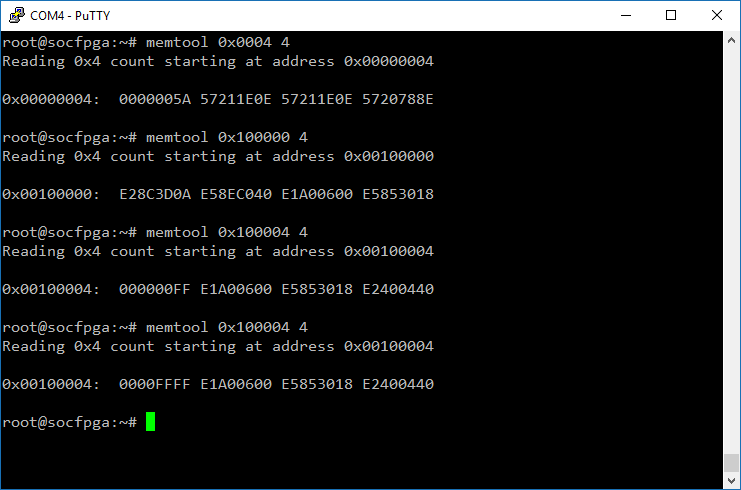

Once the board already started we can run the JTAG test again. In parallel I run some test inside Linux using memtool to test if the Linux kernel sees the same values as the FPGA does. This show how the FPGA have a transparent access to data in memory and we corroborate it checking for the same memory address inside Linux.

Now you can use any other project of your own that make use of the f2sdram interface. You should only be careful to keep compatibility with the default bus type of GHRD project (Avalon-MM Master 256 bits) and always remember to start the interface with an rbf file before Linux starts.

References

These are some helpful links that pointed me in the right direction,

- Terasic DE10-Nano Kit Resources webpage.

- JTAG to Avalon master bridge usage - Altera Forums

- With the Cyclone V SoC, how can I use the FPGA fabric to access the HPS DMA? - LINK

- How can I enable the FPGA2SDRAM bridge on Cyclone V SOC and Arria V SOC devices? (Intel FPGA support) - LINK

I gave you an upvote!

Please give me a follow and take a moment to read this post regarding commenting and spam.

(tl;dr - if you spam, you will be flagged!)✅ @banzaycl, congratulations on making your first post!

Congratulations @banzaycl! You have completed some achievement on Steemit and have been rewarded with new badge(s) :

Click on any badge to view your own Board of Honor on SteemitBoard.

For more information about SteemitBoard, click here

If you no longer want to receive notifications, reply to this comment with the word

STOPCongratulations @banzaycl! You received a personal award!

You can view your badges on your Steem Board and compare to others on the Steem Ranking

Do not miss the last post from @steemitboard:

Vote for @Steemitboard as a witness to get one more award and increased upvotes!